Hello Dear Reader,

Here in this post, I will give an idea about how HLS(High-Level Synthesis) works. Here This kind of higher-level language to HDL conversion facility is provided by one of the famous software MATLAB. Here I have implemented a full-adder logic functionality to test the steps. So Let's see how it work.

Steps:

1) Open MATLAB

2) Write a function that you want to convert to VHDL

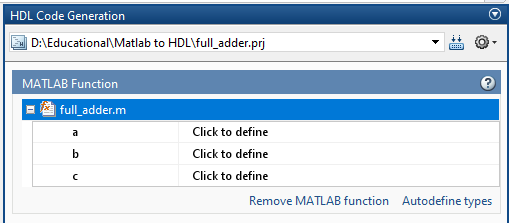

4) Open HDL Coder and make a new project

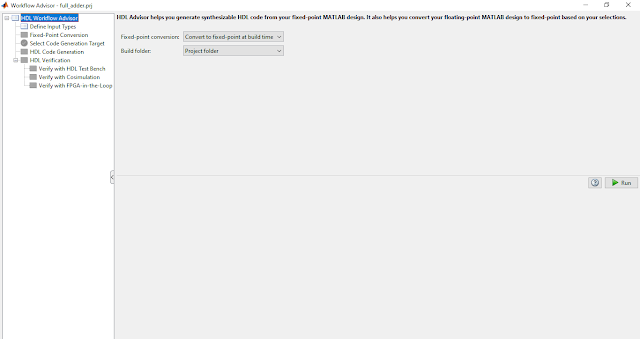

10) Go to Data collection and Compute Derived Ranges

Select VHDL as an HDL format for RTL conversion. And the last step is to press the run menu which is situated middle of the right side.

Here below is the VHDL code which is obtained from the above steps which say our steps are successfully implemented.

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

USE IEEE.numeric_std.ALL;

ENTITY full_adder_fixpt IS

PORT( a : IN std_logic;

b : IN std_logic;

c : IN std_logic;

carry : OUT std_logic;

sum : OUT std_logic

);

END full_adder_fixpt;

ARCHITECTURE rtl OF full_adder_fixpt IS

BEGIN

--HDL code generation from MATLAB function: full_adder_fixpt

--%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%

-- %

-- Generated by MATLAB 9.4 and Fixed-Point Designer 6.1 %

-- %

--%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%

sum <= ((((( NOT a) AND ( NOT b)) AND c) OR ((( NOT a) AND b) AND ( NOT c))) OR ((a AND ( NOT b)) AND ( NOT c))) OR ((a AND b) AND c);

carry <= ((a AND b) OR (b AND c)) OR (a AND c);

END rtl;

Connect with me

Superb easy explanation for this awaiting topic.

ReplyDeleteCompleted sir this steps best learning thanks for your efforts.

ReplyDeleteFirst ever I found this solution

ReplyDelete